## **Microprocessor and Microcontroller**

## **LECTURE NOTES**

**Department of Electronics and Communication Engineering**

**BY: ANURAG SETHY (LECTURER)**

**UGMIT RAYAGADA**

# Unit -1

### **Microprocessor and Microcomputer:**

### Microprocessor:

The processor on a single chip is called a Microprocessor which can process micro-instructions. Instructions in the form of 0sand 1s are called micro-instructions. The microprocessor is the CPU part of a microcomputer, and it is also available as a single integrated circuit. Thus as main components, the microprocessor will have theControl Unit (CU) and the Arithmetic Logic Unit (ALU) of a microcomputer. An example is Intel 8085 microprocessor. In addition to the microprocessor features, a microcomputer will have the following additional features:

- ROM/PROM/EPROM/EEPROM for storing program;

- RAM for storing data, intermediate results, and final results;

- I/O devices for communication with the outside world;

- I/O ports for communication with the I/O devices.

### Microcomputer:

A microcomputer can be defined as a small sized, inexpensive, and limited capability computer. It has the same architectural block structure that is present on a computer. Present-day microcomputers are having smaller sizes. Nowadays, they are of the size of a notebook. But in the coming days also their sizes will get more reduced as well. Due to their lower costs, individuals can possess them as their personal computers. Because of mass production, they are becoming still cheaper. Initially, in the earlier days, they were not very much powerful. Their internal operations and instructions were very much limited and restricted. But at present days, microcomputers have not only multiplied and divide instructions on unsigned and signed numbers but are also capable of performing floating point arithmetic operations

| Microprocessor                                                                                                                                            | Micro computer                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>it is a standalone device</li> <li>microprocessor doesn't have memory inside it to use memory it is connected by address and data bus</li> </ul> | <ul> <li>Microcomputer is a miniature<br/>computer whis has microprocessor as<br/>well as other peripheral devices.</li> <li>Microcomputer has rom and ram<br/>inside itself.</li> </ul> |

| .,                                                                                                                                                        |                                                                                                                                                                                          |

### **Evolution of Microprocessor:**

1. **4-bit Microprocessor:** The first microprocessor (Intel 4004) was invented in 1971. It was a 4-bit calculation device with a speed of 108 kHz. Since then, microprocessor power has grown exponentially. It has 3200 PMOS transistors. It is a 4-bit device used in calculator.

### 2. 8-Bit microprocessor:

In 1972, Intel came out with the 8008 which is 8-bit. In 1974, Intel announced the 8080 followed by 8085 i.e a 8-bit processor 8085 processor has 8 bit ALU (Arithmetic Logic unit). Similarly 8086 processor has 16 bit ALU. This had a larger instruction set then 8080. used NMOS transistors, so it operated much faster than the 8008. The 8080 is referred to as a "Second generation Microprocessor".

### 3. Third Generation (16 - bit Microprocessor):

The third generation microprocessors, introduced in 1978 were represented by Intel's 8086, Zilog Z800 and 80286, which were 16 - bit processors with a performance like minicomputers.

### 4. Fourth Generation (32 - bit Microprocessors): Several different companies introduced the 32-bit microprocessors, but the most popular one is the Intel 80386. It has around 275000 transitors.

### 5. Fifth Generation (64 - bit Microprocessors):

From 1995 to now we are in the fifth generation. After 80856, Intel came out with a new processor namely Pentium processor followed by **Pentium Pro CPU**, which allows multiple CPUs in a single system to achieve multiprocessing. Other improved 64-bit processors are **Celeron**, **Dual**, **Quad**, **Octa Core processors**.

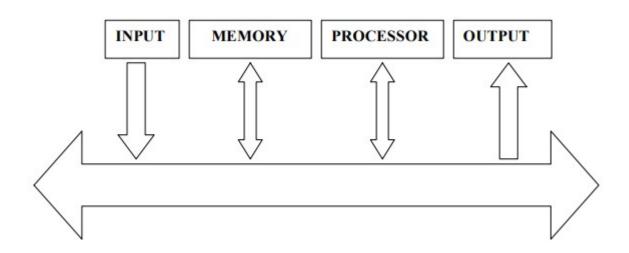

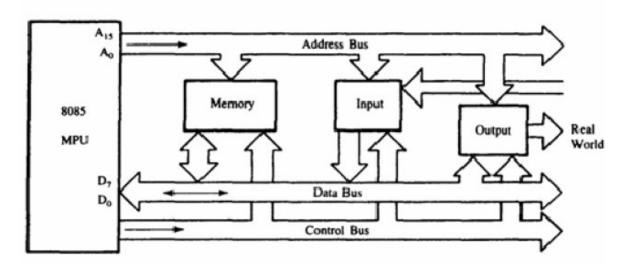

### **Bus structure:**

The simplest and most common way of interconnecting various parts of the computer. To achieve a reasonable speed of operation, a computer must be organized so that all its units can handle one full word of data at a given time. A group of lines that serve as a connecting port for several devices is called a bus. In addition to the lines that carry the data, the bus must have lines for address and control purpose. Simplest way to interconnect is to use the single bus as shown

Since the bus can be used for only one transfer at a time, only two units can actively use the bus at any given time. Bus control lines are used to arbitrate multiple requests for use of one bus.

### Address Bus:

- The address bus is a group of 16 lines generally identified as A0 to A15.

- The address bus is unidirectional: bits flow in one direction-from the MPU to peripheral devices.

- The MPU uses the address bus to perform the first function: identifying a peripheral or a memory location.

### Data bus:

- The data bus is a group of eight lines used for data flow.

- These lines are bi-directional data flow in both directions between the MPU and memory and peripheral devices.

- The MPU uses the data bus to perform the second function: transferring binary information.

- The eight data lines enable the MPU to manipulate 8-bit data ranging from 00H to FFH (2<sup>8</sup> = 256 numbers).

- The largest number that can appear on the data bus is 11111111 i.e OFFH.

### **Control Bus:**

- The control bus carries synchronization signals and providing timing signals.

- The MPU generates specific control signals for every operation it performs. These signals are used to identify a device type with which the MPU wants to communicate.

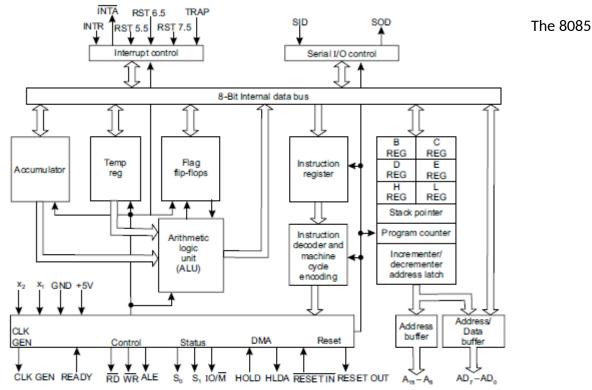

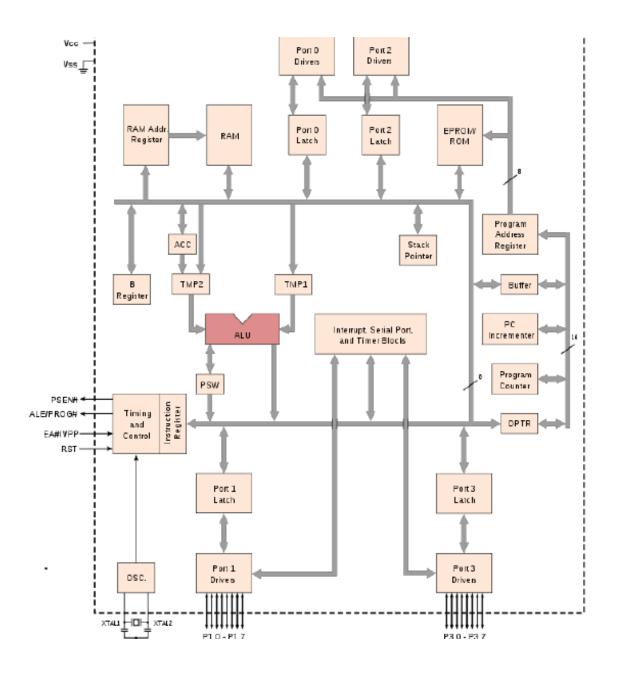

### Architecture of 8085 (8 bit) Microprocessor

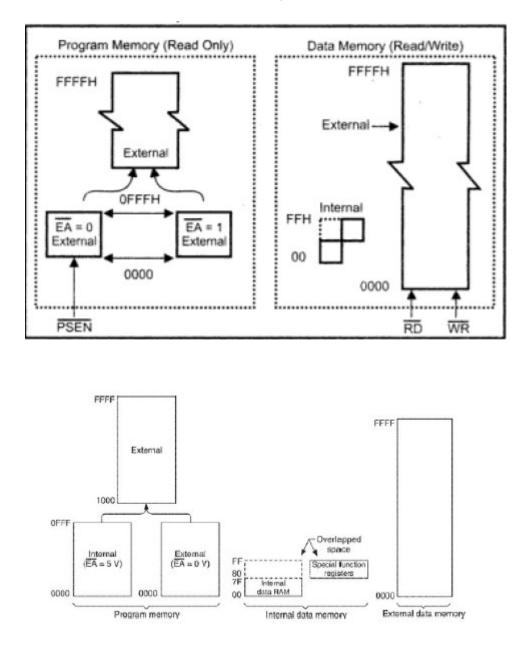

microprocessor is an 8-bit processor available as a 40-pin IC package and uses +5 V for power. It can run at a maximum frequency of 3 MHz. Its data bus width is 8-bit and address bus width is 16-bit, thus it can address 216 = 64 KB of memory. The internal architecture of 8085 is shown in above figure.

### Arithmetic and Logic Unit:

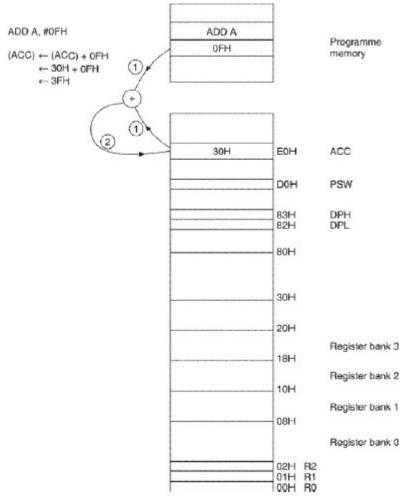

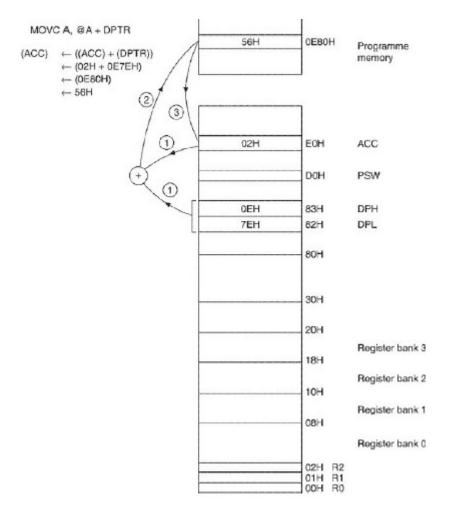

The ALU performs the actual numerical and logical operations such as Addition (ADD), Subtraction (SUB), AND, OR etc. It uses data from memory and from Accumulator to perform operations. The results of the arithmetic and logical operations are stored in the accumulator.

### **Registers** :

The 8085 includes six registers, one accumulator and one flag register, as shown in Fig. 3. In addition, it has two 16-bit registers: stack pointer and program counter. They are briefly described as follows. The 8085 has six general-purpose registers to store 8-bit data; these are identified as B, C, D, E, H and L. they can be combined as register pairs - BC, DE and HL to perform some 16-bit operations. The programmer can use these registers to store or copy data into the register by using data copy instructions.

| S. No. | Name of the Register                            | Quantity | Capacity   |

|--------|-------------------------------------------------|----------|------------|

| 1.     | Accumulator (or) Register A                     | 1        | 8-bit      |

| 2.     | Temporary register                              | 1        | 8-bit      |

| 3.     | General purpose registers (B, C, D, E, H and L) | 6        | 8-bit each |

| 4.     | Stack pointer (SP)                              | 1        | 16-bit     |

| 5.     | Program counter (PC)                            | 1        | 16-bit     |

| 6.     | Instruction register                            | 1        | 8-bit      |

| 7.     | Incrementer/Decrementer address latch           | 1        | 16-bit     |

| 8.     | Status flags register                           | 1        | 8-bit      |

### Accumulator:

The accumulator is an 8-bit register that is a part of ALU. This register is used to store 8-bit data and to perform arithmetic and logical operations. The result of an operation is stored in the accumulator. The accumulator is also identified as register A.

### Flag register:

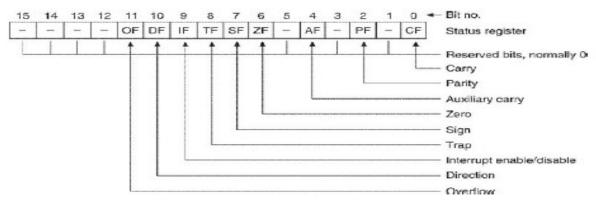

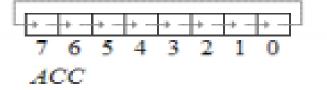

The ALU includes five flip-flops, which are set or reset after an operation according to data condition of the result in the accumulator and other registers. They are called Zero (Z), Carry (CY), Sign (S), Parity (P) and Auxiliary Carry (AC) flags. Their bit positions in the flag register are shown in Fig. 4. The microprocessor uses these flags to test data conditions.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | _ |

|----|----|----|----|----|----|----|----|---|

| S  | Z  | х  | AC | х  | Р  | х  | CY |   |

**Sign (S) flag**: – If the MSB of the result of an operation is 1, this flag is set, otherwise it is reset.

Zero (Z) flag:- If the result of an instruction is zero, this flag is set, otherwise reset.

**Auxiliary Carry (AC ) flag:-** If there is a carry out of bit 3 and into bit 4 resulting from the execution of an arithmetic operation, it is set otherwise reset. This flag is used for BCD operation and is not available to the programmer to change the sequence of an instruction.

**Carry (CY) flag**:- If an instruction results in a carry (for addition operation) or borrow (for subtraction or comparison) out of bit D7, then this flag is set, otherwise reset.

**Parity (P) flag:** This flag is set when the result of an operation contains an even number of 1's and is reset otherwise.

**Program Counter (PC)**:

This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer. The microprocessor uses this register to sequence the execution of the instructions. The function of the program counter is to point to the memory address from which the next byte is to be fetched. When a byte is being fetched, the program counter is automatically incremented by one to point to the next memory location.

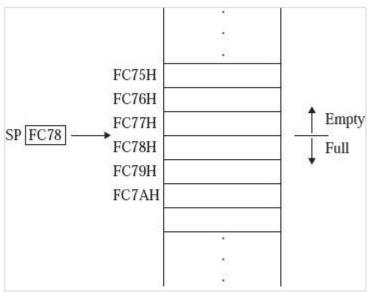

### Stack Pointer (SP) :

The Stack pointer is also a 16-bit register, used as a memory pointer. It points to a memory location in R/W memory, called stack. The beginning of the stack is defined by loading 16-bit address in the stack pointer.

### Instruction Register/Decoder:

It is an 8-bit register that temporarily stores the current instruction of a program. Latest instruction sent here from memory prior to execution. Decoder then takes instruction and decodes or interprets the instruction. Decoded instruction then passed to next stage.

### **Control Unit :**

Control Generates signals on data bus, address bus and control bus within microprocessor to carry out the instruction, which has been decoded.

**Data Bus:** Data bus carries data in binary form between microprocessor and other external units such as memory. It is used to transmit data i.e. information, results of arithmetic etc between memory and the microprocessor. Data bus is bidirectional in nature. The data bus width of 8085 microprocessor is 8-bit i.e. 28 combination of binary digits and are typically identified as D0 – D7. Thus size of the data bus determines what arithmetic can be done. If only 8-bit wide then largest number is 1111111 (255 in decimal). Therefore, larger numbers have to be broken down into chunks of 255. This slows microprocessor.

**Address Bus:** The address bus carries addresses and is one way bus from microprocessor to the memory or other devices. 8085 microprocessor contain 16-bit address bus and are generally identified as A0 - A15. The higher order address lines (A8 – A15) are unidirectional and the lower order lines (A0 – A7) are multiplexed (time-shared) with the eight data bits (D0 – D7) and hence, they are bidirectional.

**Control Bus:** Control bus are various lines which have specific functions for coordinating and controlling microprocessor operations. The control bus carries control signals partly unidirectional and partly bidirectional. The following control and status signals are used by 8085 processor:

**ALE (output):** Address Latch Enable is a pulse that is provided when an address appears on the AD0 – AD7 lines, after which it becomes 0.

$\overrightarrow{RD}$  (active low output): The Read signal indicates that data are being read from the selected I/O or memory device and that they are available on the data bus.

$\dot{WR}$  (active low output): The Write signal indicates that data on the data bus are to be written into a selected memory or I/O location.

$IO/\dot{M}$  (output): It is a signal that distinguished between a memory operation and an I/O operation. When  $IO/\dot{M}=0$  it is a memory operation and  $IO/\dot{M}=1$  it is an I/O operation.

**S1 and S0 (output):** These are status signals used to specify the type of operation being performed; they are listed in Table ,

| S1 | SO | States |

|----|----|--------|

| 0  | 0  | Halt   |

| 0  | 1  | Write  |

| 1  | 0  | Read   |

| 1  | 1  | Fetch  |

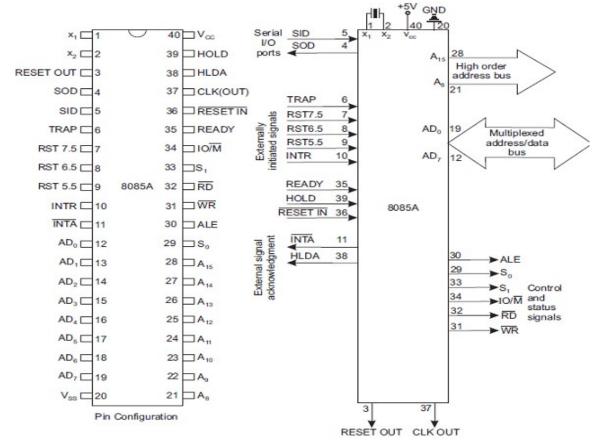

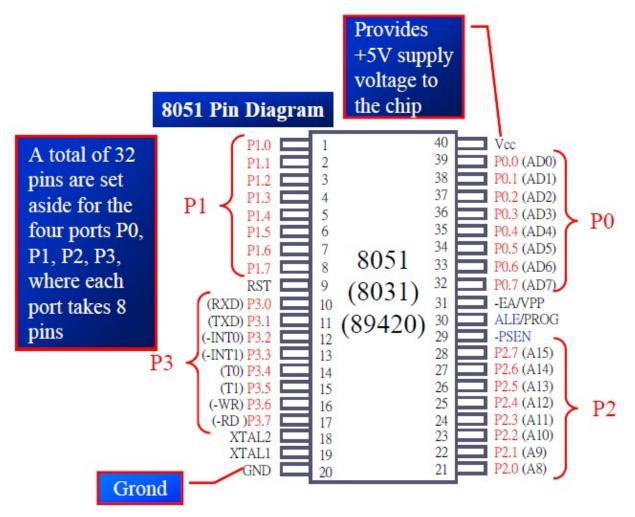

### 8085 pin diagram

### **Properties:**

• It is a 8-bit microprocessor

- Manufactured with N-MOS technology

- 40 pin IC package

- It has 16-bit address bus and thus has 216 = 64 KB addressing capability.

- Operate with 3 MHz single-phase clock

- +5 V single power supply

The logic pin layout and signal groups of the 8085nmicroprocessor are shown in Fig. 6. All the signals are classified into six groups:

- Address bus

- Data bus

- Control & status signals

- Power supply and frequency signals

- Externally initiated signals

- Serial I/O signals

Address and Data Buses:

- A8 A15 (output, 3-state): Most significant eight bits of memory addresses and the eight bits of the I/O addresses. These lines enter into tri-state high impedance state during HOLD and HALT modes.

- ADO AD7 (input/output, 3-state): Lower significant bits of memory addresses and the eight bits of the I/O addresses during first clock cycle. Behaves as data bus during third and fourth clock cycle. These lines enter into tri-state high impedance state during HOLD and HALT modes.

Control & Status Signals:

- ALE: Address latch enable

- $\dot{RD}$  : Read control signal.

- $\dot{WR}$  : Write control signal.

- $IO/\dot{M}$ , S1 and S0 : Status signals.

Power Supply & Clock Frequency:

- Vcc: +5 V power supply

- Vss: Ground reference

- X1, X2: A crystal having frequency of 6 MHz is connected at these two pins.

- CLK: Clock output

Externally Initiated and Interrupt Signals:

- RESET IN: When the signal on this pin is low, the PC is set to 0, the buses are tristated and the processor is reset.

- RESET OUT: This signal indicates that the processor is being reset. The signal can be used to reset other devices.

- READY: When this signal is low, the processor waits for an integral number of

clock cycles until it goes high.

- HOLD: This signal indicates that a peripheral like DMA (direct memory access) controller is requesting the use of address and data bus.

- HLDA: This signal acknowledges the HOLD request.

- INTR: Interrupt request is a general-purpose interrupt.

- INTA : This is used to acknowledge an interrupt.

- RST 7.5, RST 6.5, RST 5,5 restart interrupt: These are vectored interrupts and have highest priority than INTR interrupt.

- TRAP: This is a non-maskable interrupt and has the highest priority.

Serial I/O Signals:

SID: Serial input signal. Bit on this line is loaded to D7 bit of register A using RIM instruction.

SOD: Serial output signal. Output SOD is set or reset by using SIM instruction.

| Difference between SPR & GPR.                                              | i                                                                        |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------|

| GPR                                                                        | SPR                                                                      |

| 8085 has 6 general purpose registers .                                     | All the registers other than gpr are known as special purpose registers. |

| General purpose registers can be used either<br>data and address register. | All specif purpose registers has some special functions                  |

|                                                                            |                                                                          |

### Difference between SPR & GPR:

### Timing and control unit:

The T&C section is a part of CPU and generates timing and control signals for execution of instructions. This section includes Clock signals, Control signals, Status signals, DMA signals as also the Reset section. This section controls fetching and decoding operations. It also generates appropriate control signals for instruction execution as also the signals required to interface external devices.

• The control and status signals are ALE,  $\dot{RD}$ ,  $\dot{WR}$ , IO/ $\dot{M}$ , S0, S1 and READY.

- The interrupt signals are TRAP, RST 7.5, RST 6.5, RST 5.5, INTR. *INTA* is an interrupt acknowledgement signal indicating that the processor has acknowledged an INTR interrupt.

- Serial I/O signals are SID and SOD

- DMA signals are HOLD and HLDA

- Reset signals are  $RESET \in i$  and RESET OUT.

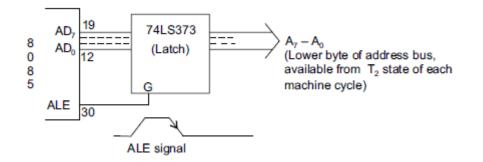

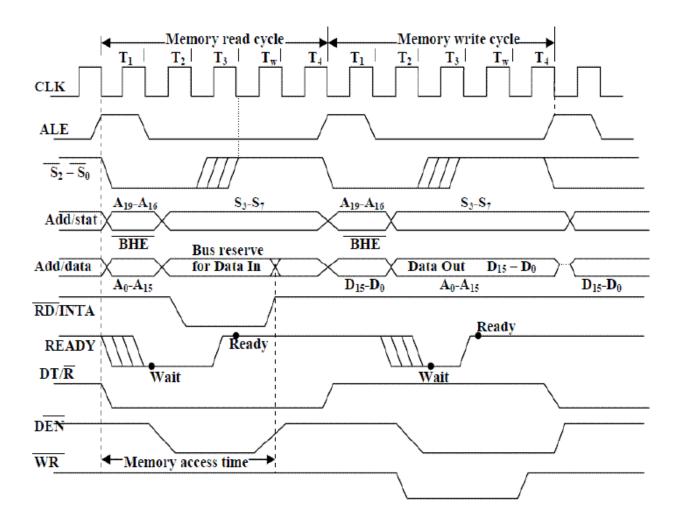

### ALE:

Pin 30 of 8085 is the ALE pin which stands for 'Address Latch Enable'. ALE signal is used to demultiplex the lower order address bus (ADO – AD7). Pins 12 to 19 of 8085 are ADO – AD7 which is the multiplexed address-data bus. Multiplexing is done to reduce the number of pins of 8085. Lower byte of address (AO – A7) are available from ADO – AD7 (pins 12 to 19) during T1 of machine cycle. But the lower byte of address (AO – A7), along with the upper byte A8 – A15 (pins 21 to 28) must be available during T2 and rest of the machine cycle to access memory location or I/O ports. Now ALE signal goes high at the beginning of T1 of each machine cycle and goes low at the end of T1 and remains low during the rest of the machine cycle. This high to low transition of ALE signal at the end of T1 is used to latch the lower order address byte (AO – A7) by the latch IC 74LS373, so that the lower byte A0 – A7 is continued to be available till the end of the machine cycle. The situation is explained in the following figure:

### DMA:

DMA mode of data transfer is fastest and pins 39 and 38 (HOLD and HLDA) become active only in this mode.

When DMA is required, the DMA controller IC (8257) sends a 1 to pin 39 of 8085. At the end of the current instruction cycle of the microprocessor it issues a1 to pin 38 of the controller. After this the bus control is totally taken over by the controller.

When 8085 is active and 8257 is idle, then the former is MASTER and the latter is SLAVE, while the roles of 8085 and 8257 are reversed when 8085 is idle and 8257 becomes active. mode of data transfer is fastest and pins 39 and 38 (HOLD and HLDA) become active only in this mode.

When DMA is required, the DMA controller IC (8257) sends a 1 to pin 39 of 8085. At the end of the current instruction cycle of the microprocessor it issues a1 to pin 38 of the controller. After this the bus control is totally taken over by the controller. When 8085 is active and 8257 is idle, then the former is MASTER and the latter is SLAVE, while the roles of 8085 and 8257 are reversed when 8085 is idle and 8257 becomes active.

$IO/\dot{M}$  signal indicates whether I/O or memory operation is being carried out. A high on this signal indicates I/O operation while a low indicates memory operation. S0 and S1 indicate the type of machine cycle in progress.

$RESET \in \dot{i}$  It is an input signal which is active when its status is low. When this pin is low, the following occurs:

- The program counter is set to zero (0000H).

- Interrupt enable and HLDA F/Fs are resetted.

- All the buses are tri-stated.

- Internal registers of 8085 are affected in a random manner.

### RESET OUT:

When this signal is high, the processor is being reset. This signal is synchronised to the processor clock and is used to reset other devices which need resetting

### STACK:

Stack is a reserved of memory used to keep track of a program's internal operations, including functions, return addresses, passed parameters ed parameters, etc. A stack is usually maintained as a "last in, first out" (LIFO) data s ) data structure, so that the last item added to the structure is the first item used. Sometimes it is useful to have region of memory for temporary storage, which does not have to be allocated named variables. When we use subroutines and interrupts it will be essential to have such a storage region. Such region is called a Stack

**The Stack Pointer** register will hold the address of the top location of the stack. And the program counter is a register always it will hold the address of the memory location from where the next instruction for execution will have to be fetched. The complete programmer's view of 8085 is shown in the following figure

| 81   | its 8    | bits         |

|------|----------|--------------|

| A    | ΞÈ       | F            |

| В    |          | C            |

| D    |          | E            |

| H    |          | L            |

| PC 🗌 |          |              |

| SP 🗌 |          |              |

| +    | -16 bits | ; <b>—</b> • |

SP is a special purpose 16-bit register. It contains a memory address. Suppose SP contents are FC78H, then the 8085 interprets it as follows

Memory locations FC78H, FC79H, ..., FFFFH are having useful information. In other words, these locations are treated as filled locations. Memory locations FC77H, FC76H, ..., 0000H are not having any useful information. In other words, these locations are treated as empty locations.

On a stack, we can perform two operations. PUSH and POP. In case of PUSH operation, the SP register gets decreased by 1 and new data item used to insert on to the top of the stack. On the other hand, in case of POP operation, the data item will have to be deleted from the top of the stack and the SP register will get increased by the value of 1.

Thus, the contents of SP specify the top most useful location in the stack. This is known as **stacktop** .In other words, it indicates the memory location with the smallest address having useful information. This is pictorially represented in the following figure –

Fig. Interpretation of SP contents

### 8085 Interrupts:

Six signals are associated with interrupt logic. There are five interrupt request pins through which the 8085 may be interrupted. These are TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR. The first four interrupts (TRAP, RST 7.5, RST 6.5, RST 5.5) are supported by hardware implemented vectoring, i.e. the locations of Interrupt Service Routines(ISR) in memory for these interrupts are fixed and automatic vectoring to the location takes place whenever any of these four interrupts is recognized. The interrupt service routine locations for these interrupts are as follows:

| Interrupt | ISR location |

|-----------|--------------|

| TRAP      | 24H          |

| RST 7.5   | 3CH          |

| RST 6.5   | 34H          |

| RST 5.5   | 2CH          |

The last interrupt INTR is a general-purpose interrupt The interrupt request on this line is acknowledged by the 8085 on the output line. On receiving the acknowledgement, the interrupting device places on the data bus the address of Interrupt Service Routine (ISR) in the memory. The microprocessor executes the ISR to service the interrupt. There are two ways by which the interrupting device can send the ISR address. It can input one byte code of one of the "RST n" instructions (RST 0 to RST 7). **These are other wise known as software interrupts**. The microprocessor will execute this instruction to branch to ISR at 8 bit address location. The RST n is a single byte subroutine call instruction. Another way is to input a 3-byte code for "CALL addr16" instruction. On receiving this 3-byte code, the microprocessor will execute this instruction to branch to ISR at addr16.

The vector address for a software interrupt is calculated as follows:

Vector address = interrupt number × 8

For example, the vector address for RST 5 is calculated as

$5 \times 8 = (40)_{10} = (28)_{H}$

Vector address for RST 5 is 0028H.

| Instruction | Corresponding<br>HEX code | Vector<br>addresses |

|-------------|---------------------------|---------------------|

| RST 0       | C7                        | 0000H               |

| RST 1       | CF                        | 0008H               |

| RST 2       | D7                        | 0010H               |

| RST 3       | DF                        | 0018H               |

| RST 4       | E7                        | 0020H               |

| RST 5       | EF                        | 0028H               |

| RST 6       | F7                        | 0030H               |

| RST 7       | FF                        | 0038H               |

TRAP interrupt is the non-maskable interrupt for 8085. It means that if an interrupt comes via TRAP, 8085 will have to recognise the interrupt.

Interrupts INTR, RST 5.5 and RST 6.5 are level-triggered, i.e. a high signal should be present on these lines when the interrupt is recognized. In other words, if a device sends an interrupt pulse of short duration on any of these lines, it is possible that this interrupt request is ignored totally owing to the reason that the interrupt pulse may not be present when these lines are scanned by the microprocessor for the interrupt request. RST 7.5 is edge-triggered and TRAP is level- as well as edge-triggered. Both are associated with internal latches which store the interrupt

requests as and when the interrupt signal on these lines goes from low to high. TRAP is normally reserved for power failure or some other highest priority interrupt. Thus, it will be desirable to protect this pin from spurious signals. It is because of this reason that TRAP is level as well as edge-triggered.

The interrupts of 8085 have their priorities fixed—TRAP interrupt has the highest priority, followed by RST 7.5, RST 6.5, RST 5.5 and lastly INTR.

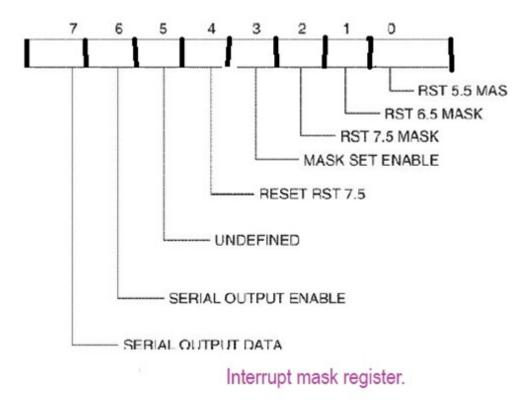

#### Interrupt masking:

An interrupt which can be disabled by software means, is called a maskable interrupt. Thus an interrupt which cannot be masked is an unmaskable interrupt. Various interrupts can be enabled or disabled selectively by masking. There is an interrupt mask register in the interrupt control system Various bits of this register are used for enabling or disabling of interrupts. The first 3 bits—bit 0, bit 1, and bit 2—are devoted to interrupt masks for RST 5.5, RST 6.5 and RST 7.5 interrupts respectively. If any of these bits is set to 1, the particular interrupt is disabled, otherwise it is enabled. Bit 3 is the overriding bit for bit 0, bit 1, and bit 2. This bit is called the Mask Set Enable (MSE). Only when this bit is set to 1, the mask bits for interrupts RST 5.5, RST 6.5, and RST 7.5 are taken into consideration. Bit 4 is used to reset the RST 7.5 latch. When this bit is set to 1, the latch associated. with the RST 7.5 interrupt is regardless of whether RST 7.5 is masked or not. Bit 5 is not used. Bit 6 and bit 7 are devoted to serial output; these bits are discussed under Section 3.2.7 on Serial Input- Output. All the interrupts can also be reset/disabled through the signal at  $RESET \in i$ .

To mask any interrupt, the user will set the bit pattern in accumulator (ACC) according to his need and execute the SIM (Set Interrupt Mask) instruction. As an example, if we want to enable RST 7.5 and RST 5.5 and disable RST 6.5, the bit pattern will be

#### 00011010=1AH

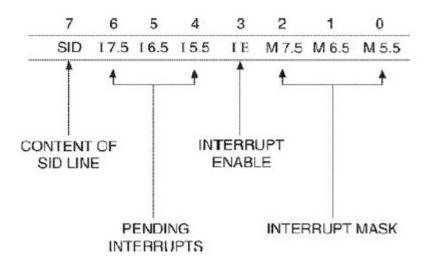

The user will transfer 1AH to ACC and execute the SIM instruction. The user will often wish to know about the status of the various interrupts, i.e. whether they are enabled and whether any interrupt is pending on these lines. This is facilitated by the RIM (Read Interrupt Mask) instruction. This instruction when executed, loads the accumulatorwith a byte—the structure of which is shown inbelow Figure. Bit 0, bit 1, and bit 2 of this byte indicate interrupt masks set for interrupts RST 5.5, RST 6.5, and RST 7.5 respectively. Bit 3 shows whether the interrupt system is enabled or disabled. The next three bits indicate whether any interrupt is pending on RST 5.5, RST 6.5, and RST 7.5 respectively. Bit7 is reserved for serial input data. The user will examine the status of various interrupts and then take appropriate decision to mask or unmask any interrupt.

## **Microprocessor and Microcontroller**

## **LECTURE NOTES**

**Department of Electronics and Communication Engineering**

**BY: ANURAG SETHY (LECTURER)**

**UGMIT RAYAGADA**

## UNIT-2

### **Instruction Word Size in Microprocessor**

The 8085 instruction set is classified into 3 categories by considering the length of the instructions. In 8085, the length is measured in terms of "byte" rather then "word" because 8085 microprocessor has 8-bit data bus. Three types of instruction are: 1-byte instruction, 2-byte instruction, and 3-byte instruction.

### 1. One-byte instructions:

In 1-byte instruction, the opcode and the operand of an instruction are represented in one byte.

### Example-1

Mnemonic- MOV B, A Opcode- MOV Operand- B, A Hex Code- 47H Binary code- 0100 0111

### • Example-2:

Task- Add the contents of accumulator to the contents of register B.

Mnemonic- ADD B Opcode- ADD Operand- B Hex Code- 80H Binary code- 1000 0000

#### 2. Two-byte instructions

Two-byte instruction is the type of instruction in which the first 8 bits indicates the opcode and the next 8 bits indicates the operand.

#### Example-1:

Task- Load the hexadecimal data 32H in the accumulator.

```

Mnemonic- MVI A, 32H

Opcode- MVI

Operand- A, 32H

Hex Code- 3E

32

Binary code- 0011 1110

0011 0010

```

### 3. Three-byte instructions

Three-byte instruction is the type of instruction in which the first 8 bits indicates the opcode and the next two bytes specify the 16-bit address. The low-order address is represented in second byte and the high-order address is represented in the third byte.

### • Example-1:

Task- Load contents of memory 2050H in the accumulator.

```

Mnemonic- LDA 2050H

Opcode- LDA

Operand- 2050H

Hex Code- 3A

50

20

Binary code- 0011 1010

0101 0000

0010 0000

```

### • Example-2:

Task- Transfer the program sequence to the memory location 2050H.

```

Mnemonic- JMP 2085H

Opcode- JMP

Operand- 2085H

Hex Code- C3

85

20

Binary code- 1100 0011

1000 0101

0010 0000

```

### 8085 Addressing Modes

The process of specifying the data to be operated on by the instruction is called addressing. The various formats for specifying operands are called addressing modes. The 8085 has the following five types of addressing:

I. Immediate addressingII. Memory direct addressingIII. Register direct addressingIV. Indirect addressingV. Implicit addressing

### **Immediate Addressing:**

In this mode, the operand given in the instruction - a byte or word - transfers to the destination register or memory location. Ex: MVI A, 9AH The operand is a part of the instruction. The operand is stored in the register mentioned in the instruction.

### Memory Direct Addressing:

Memory direct addressing moves a byte or word between a memory location and register. The memory location address is given in the instruction. Ex: LDA 850FH

This instruction is used to load the content of memory address 850FH in the accumulator.

### **Register Direct Addressing:**

Register direct addressing transfer a copy of a byte or word from source register to destination register.

Ex: MOV B, C

It copies the content of register C to register B.

### Indirect Addressing:

Indirect addressing transfers a byte or word between a register and a memory location. Ex: MOV A, M

Here the data is in the memory location pointed to by the contents of HL pair. The data is moved to the accumulator

### Implicit Addressing

In this addressing mode the data itself specifies the data to be operated upon.

Ex: CMA

The instruction complements the content of the accumulator. No specific data or operand is mentioned in the instruction

### 8085 Instruction Set

### **DATA TRANSFER INSTRUCTIONS**

| Opcode | Operand                  | Description                                                                                                                                                                                                                                                                                                        |

|--------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV    | Rd, Rs<br>M, Rs<br>Rd, M | This instruction copies the<br>contents of the source<br>register into the destination<br>register; the contents of the<br>source register are not altered.<br>If one of the operands is a<br>memory location, its location is<br>specified by the contents of<br>the HL registers<br>Example: MOV B, C or MOV B,M |

| MVI    | Rd, data<br>M, data      | The 8-bit data is stored in the<br>destination register or<br>memory. If the operand is a<br>memory location, its location is<br>specified by the contents of the<br>HL registers.<br>Example: MVI B, 57H or MVI M,<br>57H                                                                                         |

| LDA    | 16-bit address           | The contents of a memory<br>location, specified by a<br>16-bit address in the operand,<br>are copied to the accumulator.<br>The contents of the source are<br>not altered.<br>Example: LDA 2034H                                                                                                                   |

| LDAX   | B/D Reg. pair            | The contents of the designated<br>register pair point to a memory<br>location. This instruction copies<br>the contents of that memory<br>location into the accumulator.<br>The contents of either the<br>register pair or the memory                                                                               |

|      |                        | location are not altered.<br>Example: LDAX B                                                                                                                                                                                                                                                                                                                                 |

|------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LXI  | Reg. pair, 16-bit data | The instruction loads 16-bit data<br>in the register pair<br>designated in the operand.<br>Example: LXI H, 2034H or LXI H,<br>XYZ                                                                                                                                                                                                                                            |

| LHLD | 16-bit address         | The instruction copies the<br>contents of the memory<br>location<br>pointed out by the 16-bit<br>address into register L and<br>copies<br>the contents of the next<br>memory location into register H.<br>The<br>contents of source memory<br>locations are not altered.<br>Example: LHLD 2040H                                                                              |

| STA  | 16-bit address         | The contents of the accumulator<br>are copied into the memory<br>location specified by the<br>operand. This is a 3-byte<br>instruction,<br>the second byte specifies the<br>low-order address and the third<br>byte specifies the high-order<br>address.<br>Example: STA 4350H                                                                                               |

| SHLD | 16-bit address         | The contents of register L are<br>stored into the memory location<br>specified by the 16-bit address<br>in the operand and the contents<br>of H register are stored into the<br>next memory location by<br>incrementing the operand. The<br>contents of registers HL are<br>not altered. This is a 3-byte<br>instruction, the second byte<br>specifies the low-order address |

|      |           | and the third byte specifies the<br>high-order address.<br>Example: SHLD 2470H                                                                                                                                                                                                                                                     |

|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STAX | Reg. pair | The contents of the accumulator<br>are copied into the memory<br>location specified by the<br>contents of the operand<br>(register<br>pair). The contents of the<br>accumulator are not altered.<br>Example: STAX B                                                                                                                |

| XCHG |           | The contents of register H are<br>exchanged with the contents of<br>register D, and the contents of<br>register L are exchanged with<br>the contents of register E.<br>Example: XCHG                                                                                                                                               |

| SPHL |           | The instruction loads the<br>contents of the H and L registers<br>into<br>the stack pointer register, the<br>contents of the H register<br>provide the high-order address<br>and the contents of the L<br>register provide the low-order<br>address. The contents of the H<br>and L registers are not altered.<br>Example: SPHL    |

| XTHL |           | The contents of the L register<br>are exchanged with the stack<br>location pointed out by the<br>contents of the stack pointer<br>register. The contents of the H<br>register are exchanged with<br>the next stack location (SP+1);<br>however, the contents of the<br>stack pointer register are not<br>altered.<br>Example: XTHL |

| PUSH | Reg. pair | The contents of the register pair<br>designated in the operand are                                                                                                                                                                                                                                                                 |

|     |                    | copied onto the stack in the<br>following sequence. The stack<br>pointer register is decremented<br>and the contents of the<br>highorder<br>register (B, D, H, A) are copied<br>into that location. The<br>stack pointer register is<br>decremented again and the<br>contents of<br>the low-order register (C, E, L,<br>flags) are copied to that<br>location.<br>Example: PUSH B or PUSH A                                       |

|-----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POP | POP Reg. pair      | The contents of the memory<br>location pointed out by the<br>stack<br>pointer register are copied to<br>the low-order register (C, E, L,<br>status flags) of the operand. The<br>stack pointer is incremented<br>by 1 and the contents of that<br>memory location are copied to<br>the high-order register (B, D, H,<br>A) of the operand. The stack<br>pointer register is again<br>incremented by 1.<br>Example: POP H or POP A |

| OUT | 8-bit port address | The contents of the accumulator<br>are copied into the I/O port<br>specified by the operand.<br>Example: OUT F8H                                                                                                                                                                                                                                                                                                                  |

| IN | 8-bit port address | The contents of the input port<br>designated in the operand are<br>read and loaded into the<br>accumulator.<br>Example: IN 8CH |

|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

|    |                    |                                                                                                                                |

### ARITHMETIC INSTRUCTIONS

| Opcode                                  | Operand                            | Description                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add regis<br>ADD                        | ter or memory to accumul<br>R<br>M | ator<br>The contents of the operand (register or memory) are<br>added to the contents of the accumulator and the result is<br>stored in the accumulator. If the operand is a memory<br>location, its location is specified by the contents of the HL<br>registers. All flags are modified to reflect the result of the<br>addition.<br>Example: ADD B or ADD M            |

| Add regis                               | ter to accumulator with ca         | ny                                                                                                                                                                                                                                                                                                                                                                        |

| ADC                                     | R<br>M                             | The contents of the operand (register or memory) and<br>the Carry flag are added to the contents of the accumulator<br>and the result is stored in the accumulator. If the operand is a<br>memory location, its location is specified by the contents of<br>the HL registers. All flags are modified to reflect the result of<br>the addition.<br>Example: ADC B or ADC M |

| Add imm                                 | ediate to accumulator              |                                                                                                                                                                                                                                                                                                                                                                           |

| ADI                                     | 8-bit data                         | The 8-bit data (operand) is added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition. Example: ADI 45H                                                                                                                                                                          |

| Add immediate to accumulator with carry |                                    |                                                                                                                                                                                                                                                                                                                                                                           |

| ACI                                     | 8-bit data                         | The 8-bit data (operand) and the Carry flag are added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition.                                                                                                                                                                       |

Example: ACI 45H

Add register pair to H and L registers DAD Reg. pair The 16-bit contents of the specified register pair are added to the contents of the HL register and the sum is stored in the HL register. The contents of the source register pair are not altered. If the result is larger than 16 bits, the CY flag is set. No other flags are affected. Example: DAD H Subtract register or memory from accumulator SUB The contents of the operand (register or memory ) are R Μ subtracted from the contents of the accumulator, and the result is stored in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the subtraction. Example: SUB B or SUB M Subtract source and borrow from accumulator SBB R The contents of the operand (register or memory ) and Μ the Borrow flag are subtracted from the contents of the accumulator and the result is placed in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the subtraction. Example: SBB B or SBB M Subtract immediate from accumulator SUI 8-bit data The 8-bit data (operand) is subtracted from the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the subtraction. Example: SUI 45H Subtract immediate from accumulator with borrow SBI 8-bit data The 8-bit data (operand) and the Borrow flag are subtracted from the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the subtracion. Example: SBI 45H Increment register or memory by 1 INR R The contents of the designated register or memory) are М incremented by 1 and the result is stored in the same place. If the operand is a memory location, its location is specified by the contents of the HL registers. Example: INR B or INR M

Increment register pair by 1 INX R

The contents of the designated register pair are incremented by 1 and the result is stored in the same place. Example: INX H

| Decremen<br>DCR | t register or memory by 1<br>R<br>M | The contents of the designated register or memory are<br>decremented by 1 and the result is stored in the same place. If<br>the operand is a memory location, its location is specified by<br>the contents of the HL registers.<br>Example: DCR B or DCR M                                                                                     |

|-----------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Decremen        | t register pair by 1                |                                                                                                                                                                                                                                                                                                                                                |

|                 | R                                   | The contents of the designated register pair are decremented<br>by 1 and the result is stored in the same place.<br>Example: DCX H                                                                                                                                                                                                             |

| Decimal a       | djust accumulator                   |                                                                                                                                                                                                                                                                                                                                                |

|                 | none                                | The contents of the accumulator are changed from a binary value to two 4-bit binary coded decimal (BCD) digits. This is the only instruction that uses the auxiliary flag to perform the binary to BCD conversion, and the conversion procedure is described below. S, Z, AC, P, CY flags are altered to reflect the results of the operation. |

|                 |                                     | If the value of the low-order 4-bits in the accumulator is greater than 9 or if AC flag is set, the instruction adds 6 to the low-order four bits.                                                                                                                                                                                             |

|                 |                                     | If the value of the high-order 4-bits in the accumulator is greater than 9 or if the Carry flag is set, the instruction adds 6 to the high-order four bits.                                                                                                                                                                                    |

|                 |                                     | Example: DAA                                                                                                                                                                                                                                                                                                                                   |

#### BRANCHING INSTRUCTIONS

| Opcode           | Operand                        | Description                                                                                                                                          |

|------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

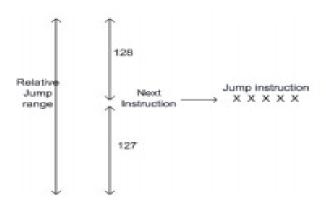

| Jump unco<br>JMP | onditionally<br>16-bit address | The program sequence is transferred to the memory location<br>specified by the 16-bit address given in the operand.<br>Example: JMP 2034H or JMP XYZ |

Jump conditionally

Operand: 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Example: JZ 2034H or JZ XYZ

| Description         | Flag Status                                                                                                                      |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Jump on Carry       | CY = 1                                                                                                                           |

| Jump on no Carry    | CY = 0                                                                                                                           |

| Jump on positive    | S = 0                                                                                                                            |

| Jump on minus       | S = 1                                                                                                                            |

| Jump on zero        | Z = 1                                                                                                                            |

| Jump on no zero     | Z = 0                                                                                                                            |

| Jump on parity even | P = 1                                                                                                                            |

| Jump on parity odd  | $\mathbf{P} = 0$                                                                                                                 |

|                     | Jump on Carry<br>Jump on no Carry<br>Jump on positive<br>Jump on minus<br>Jump on zero<br>Jump on no zero<br>Jump on parity even |

| Unconditi<br>CALL | onal subroutine call<br>16-bit address | The program sequence is transferred to the memory location                                                                   |

|-------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                   |                                        | specified by the 16-bit address given in the operand. Before<br>the transfer, the address of the next instruction after CALL |

|                   |                                        | (the contents of the program counter) is pushed onto the stack.                                                              |

|                   |                                        | Example: CALL 2034H or CALL XYZ                                                                                              |

| Call condi        | tionally                               |                                                                                                                              |

Operand: 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Before the transfer, the address of the next instruction after the call (the contents of the program counter) is pushed onto the stack. Example: CZ 2034H or CZ XYZ

| Opcode | Description         | Flag Status      |

|--------|---------------------|------------------|

| CC     | Call on Carry       | CY = 1           |

| CNC    | Call on no Carry    | CY = 0           |

| CP     | Call on positive    | S = 0            |

| CM     | Call on minus       | S = 1            |

| CZ     | Call on zero        | Z = 1            |

| CNZ    | Call on no zero     | Z = 0            |

| CPE    | Call on parity even | P = 1            |

| CPO    | Call on parity odd  | $\mathbf{P} = 0$ |

Return from subroutine unconditionally

none

The program sequence is transferred from the subroutine to the calling program. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RET

Return from subroutine conditionally

Operand: none

RET

The program sequence is transferred from the subroutine to the calling program based on the specified flag of the PSW as described below. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RZ

| Opcode | Description           | Flag Status      |

|--------|-----------------------|------------------|

| RC     | Return on Carry       | CY = 1           |

| RNC    | Return on no Carry    | CY = 0           |

| RP     | Return on positive    | S = 0            |

| RM     | Return on minus       | S = 1            |

| RZ     | Return on zero        | Z = 1            |

| RNZ    | Return on no zero     | Z = 0            |

| RPE    | Return on parity even | P = 1            |

| RPO    | Return on parity odd  | $\mathbf{P} = 0$ |

Load program counter with HL contents PCHL none The contents of registers H and L are copied into the program counter. The contents of H are placed as the high-order byte and the contents of L as the low-order byte. Example: PCHL Restart RST 0-7 The RST instruction is equivalent to a 1-byte call instruction to one of eight memory locations depending upon the number. The instructions are generally used in conjunction with interrupts and inserted using external hardware. However these can be used as software instructions in a program to transfer program execution to one of the eight locations. The addresses are: Instruction Restart Address 0000H RST 0 RST 1 0008H RST 2 0010H RST 3 0018H

RST 4

RST 5

RST 6

RST 7

The 8085 has four additional interrupts and these interrupts generate RST instructions internally and thus do not require any external hardware. These instructions and their Restart addresses are:

0020H

0028H

0030H

0038H

| Interrupt | Restart Address |

|-----------|-----------------|

| TRAP      | 0024H           |

| RST 5.5   | 002CH           |

| RST 6.5   | 0034H           |

| RST 7.5   | 003CH           |

#### LOGICAL INSTRUCTIONS

Opcode Operand Description

Compare register or memory with accumulator

| -          | register or memory with |                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMP        | R<br>M                  | The contents of the operand (register or memory) are<br>compared with the contents of the accumulator. Both<br>contents are preserved . The result of the comparison is<br>shown by setting the flags of the PSW as follows:<br>if $(A) < (reg/mem)$ : carry flag is set<br>if $(A) = (reg/mem)$ : zero flag is set<br>if $(A) > (reg/mem)$ : carry and zero flags are reset<br>Example: CMP B or CMP M |

| Compare    | immediate with accumul  | ator                                                                                                                                                                                                                                                                                                                                                                                                    |

| CPI        | 8-bit data              | The second byte (8-bit data) is compared with the contents of<br>the accumulator. The values being compared remain<br>unchanged. The result of the comparison is shown by setting<br>the flags of the PSW as follows:<br>if (A) < data: carry flag is set<br>if (A) = data: zero flag is set<br>if (A) > data: carry and zero flags are reset<br>Example: CPI 89H                                       |

| Logical A  | ND register or memory v | with accumulator                                                                                                                                                                                                                                                                                                                                                                                        |

| AÑA        | R<br>M                  | The contents of the accumulator are logically ANDed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY is reset. AC is set.<br>Example: ANA B or ANA M                   |

| Logical AN | D immediate with accum  | nulator                                                                                                                                                                                                                                                                                                                                                                                                 |

| <u> </u>   | 8-bit data              | The contents of the accumulator are logically ANDed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY is reset. AC is set.<br>Example: ANI 86H                                                                                                                                                        |

Exclusive OR register or memory with accumulator

XRA

R

Μ

The contents of the accumulator are Exclusive ORed with the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: XRA B or XRA M

| Exclusive<br>XRI  | OR immediate with accur<br>8-bit data | nulator<br>The contents of the accumulator are Exclusive ORed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: XRI 86H                                                                                                                                          |

|-------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logical O<br>ORA  | PR register or memory with<br>R<br>M  | accumulaotr<br>The contents of the accumulator are logically ORed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: ORA B or ORA M |

| Logical O<br>ORI  | R immediate with accumu<br>8-bit data | lator<br>The contents of the accumulator are logically ORed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: ORI 86H                                                                                                                                            |

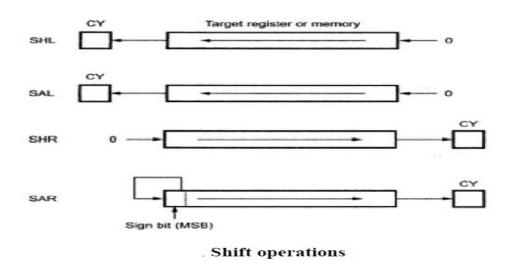

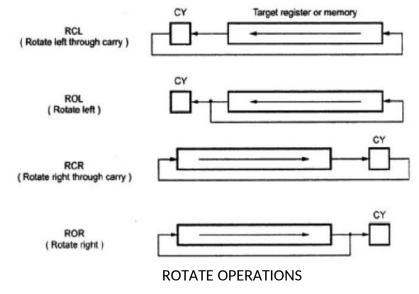

| Rotate acc<br>RLC | cumulator left<br>none                | Each binary bit of the accumulator is rotated left by one position. Bit D7 is placed in the position of $D_0$ as well as in the Carry flag. CY is modified according to bit D7. S, Z, P, AC are not affected.<br>Example: RLC                                                                                                                                                                    |

| Rotate acc<br>RRC | rumulator right<br>none               | Each binary bit of the accumulator is rotated right by one position. Bit $D_0$ is placed in the position of $D_7$ as well as in the Carry flag. CY is modified according to bit $D_0$ . S, Z, P, AC are not affected.<br>Example: RRC                                                                                                                                                            |

| Rotate acc<br>RAL | umulator left through carr<br>none    | Each binary bit of the accumulator is rotated left by one<br>position through the Carry flag. Bit D7 is placed in the Carry<br>flag, and the Carry flag is placed in the least significant<br>position D0. CY is modified according to bit D7. S, Z, P, AC<br>are not affected.                                                                                                                  |

Example: RAL

| Rotate acc<br>RAR | umulator right through ca<br>none | Each binary bit of the accumulator is rotated right by one<br>position through the Carry flag. Bit D <sub>0</sub> is placed in the Carry<br>flag, and the Carry flag is placed in the most significant<br>position D <sub>7</sub> . CY is modified according to bit D <sub>0</sub> . S, Z, P, AC<br>are not affected.<br>Example: RAR |

|-------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compleme          | ent accumulator                   |                                                                                                                                                                                                                                                                                                                                       |

| CMA               | none                              | The contents of the accumulator are complemented. No flags<br>are affected.<br>Example: CMA                                                                                                                                                                                                                                           |

| Complem           | ent carry                         |                                                                                                                                                                                                                                                                                                                                       |

| CMC               | none                              | The Carry flag is complemented. No other flags are affected.<br>Example: CMC                                                                                                                                                                                                                                                          |

| Set Carry<br>STC  | none                              | The Carry flag is set to 1. No other flags are affected.<br>Example: STC                                                                                                                                                                                                                                                              |

| CONTRO            | L INSTRUCTIONS                    |                                                                                                                                                                                                                                                                                                                                       |

.

| Opcode                    | Operand     | Description                                                                                                                                                                                                                                                                                                                           |

|---------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No operat<br>NOP          | ion<br>none | No operation is performed. The instruction is fetched and decoded. However no operation is executed. Example: NOP                                                                                                                                                                                                                     |

| Halt and enter wait state |             |                                                                                                                                                                                                                                                                                                                                       |

| HLT                       | none        | The CPU finishes executing the current instruction and halts<br>any further execution. An interrupt or reset is necessary to<br>exit from the halt state.<br>Example: HLT                                                                                                                                                             |

| Disable interrupts        |             |                                                                                                                                                                                                                                                                                                                                       |

| DI                        | none        | The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled. No flags are affected. Example: DI                                                                                                                                                                                                       |

| Enable interrupts         |             |                                                                                                                                                                                                                                                                                                                                       |

| EI                        | none        | The interrupt enable flip-flop is set and all interrupts are<br>enabled. No flags are affected. After a system reset or the<br>acknowledgement of an interrupt, the interrupt enable flip-<br>flop is reset, thus disabling the interrupts. This instruction is<br>necessary to reenable the interrupts (except TRAP).<br>Example: EI |

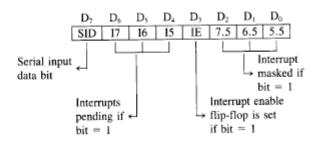

Read interrupt mask RIM none

This is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit. The instruction loads eight bits in the accumulator with the following interpretations. Example: RIM

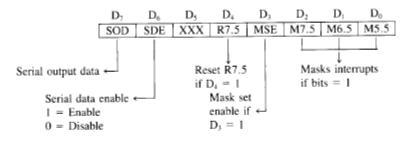

Set interrupt mask SIM none

This is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output. The instruction interprets the accumulator contents as follows. Example: SIM

- □ SOD—Serial Output Data: Bit D<sub>7</sub> of the accumulator is latched into the SOD output line and made available to a serial peripheral if bit D<sub>6</sub> = 1.

- SDE—Serial Data Enable: If this bit = 1, it enables the serial output. To implement serial output, this bit needs to be enabled.

- □ XXX Don't Care

- R7.5—Reset RST 7.5: If this bit = 1, RST 7.5 flip-flop is reset. This is an additional control to reset RST 7.5.

- □ MSE Mask Set Enable: If this bit is high, it enables the functions of bits D<sub>2</sub>, D<sub>1</sub>, D<sub>0</sub>. This is a master control over all the interrupt masking bits. If this bit is low, bits D<sub>2</sub>, D<sub>1</sub>, and D<sub>0</sub> do not have any effect on the masks.

- $\square M7.5 D_2 = 0$ , RST 7.5 is enabled.

- = 1, RST 7.5 is masked or disabled.

- $\square$  M6.5 D<sub>1</sub> = 0, RST 6.5 is enabled.

- = 1, RST 6.5 is masked or disabled.

- $\square$  M5.5—D<sub>0</sub> = 0, RST 5.5 is enabled.

- = 1, RST 5.5 is masked or disabled.

## UNIT-3

# Unit-5

## 8086 microprocessor

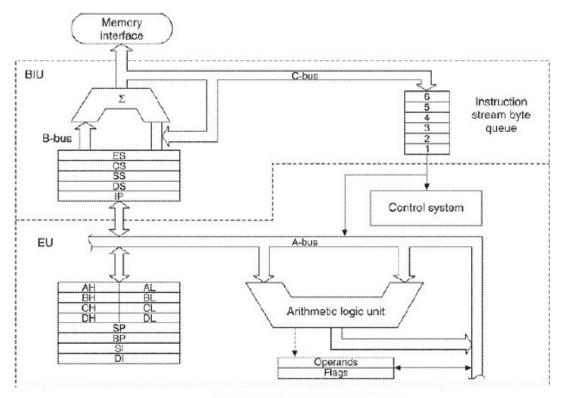

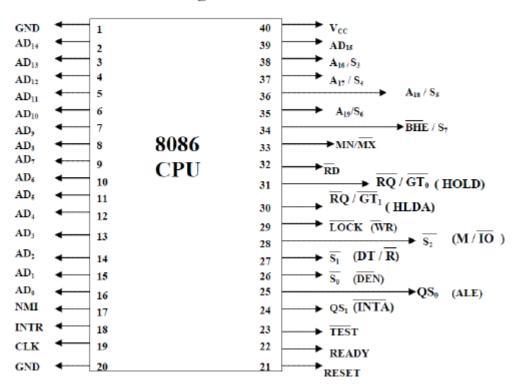

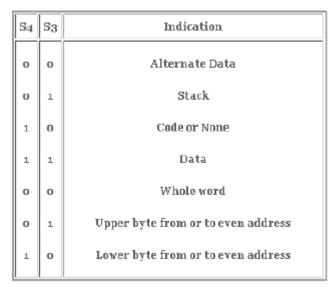

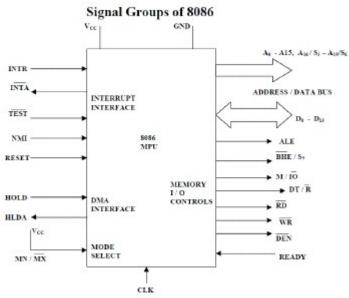

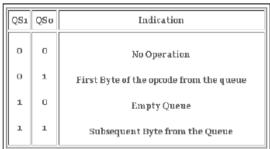

#### **Register Organization of 8086:**

General purpose registers: The 8086 microprocessor has a total of fourteen registers that are accessible to the programmer. It is divided into four groups. They are:

- Four General purpose registers

- Four Index/Pointer registers

- Four Segment registers

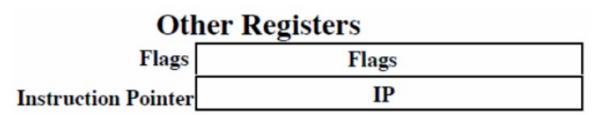

- Two Other register

### General Purpose Registers

| Accumulator | AX | 0<br>Multiply, divide, I/O      |

|-------------|----|---------------------------------|

| Base        | BX | Pointer to base addresss (data) |

| Count       | CX | Count for loops, shifts         |

| Data        | DX | Multiply, divide, I/O           |

Accumulator register consists of two 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations and string manipulation.

Base register consists of two 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BL in this case contains the low-order byte of the word, and BH contains the high-order byte. BX register usually contains a data pointer used for based, based

indexed or register indirect addressing.

Count register consists of two 8-bit registers CL and CH, which can be combined together and used as a 16-bit register CX. When combined, CL register contains the low order byte of the word, and CH contains the high-order byte. Count register can be used in Loop, shift/rotate instructions and as a counter in string manipulation.

Data register consists of two 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX. When combined, DL register contains the low order byte of the word, and DH contains the high-order byte. Data register can be used as a port number in I/O operations. In integer 32-bit multiply and divide instruction the DX register contains high-order word of the initial or resulting number.

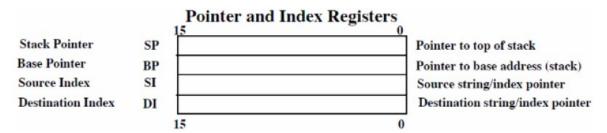

#### **Index or Pointer Registers**

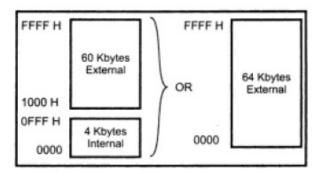

These registers can also be called as Special Purpose registers.